Download

Introducing Flex IP Solution

Flex IP Solution is a flexible modular design IP providing TSN functionality for customized chips (ASICs or ASSPs). It is extendable up to 8 ports, offers a wide range of configurable features and supports standards including IEEE TSN and HSR/PRP. Flex IP Solution is developed and optimized for use in industrial automation applications.

Flex IP Solution Building Blocks

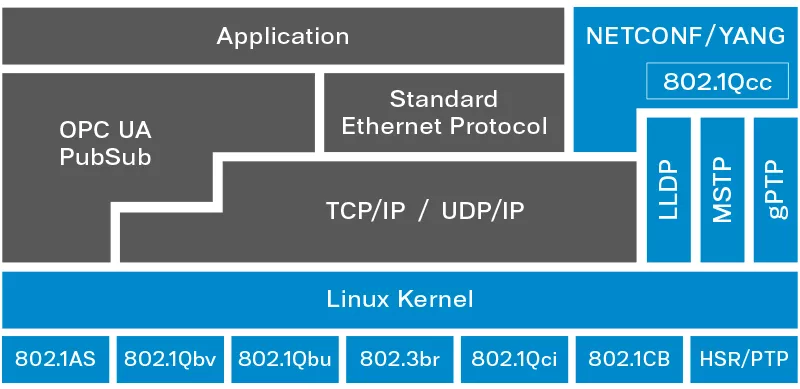

Flex IP Solution offers a customizable set of building blocks (highlighted in blue)

that enable TSN and HSR/PRP features in your chip.

Supported TSN Standards

IEEE 802.1Qbv

Time Aware Shaping

Provides guaranteed communication latency for time-critical traffic over standard Ethernet even in a converged infrastructure.

IEEE 802.1AS

Time Synchronization

Profile of IEEE 1588v2 for synchronization of clocks in the network. Supports timing requirements for scheduled TSN networks.

IEEE 802.1Qcc

SRP Enhancements

Defines the interfaces for central configuration of TSN networks. Supports configuration models for dynamic scheduling of TSN.

IEEE 802.1Qbu

Frame Preemption

Allows for optimal bandwidth utilization of non-scheduled background traffic sent in parallel with scheduled traffic.

IEEE 802.1CB

Seamless Redundancy

Enables seamless redundancy for increased network availability. Allows for redundancy on a per stream basis for individual critical streams.

IEEE 802.1Qci

Filtering and Policing

Protects against faulty and/or malicious endpoints and switches. Isolates faults to specific regions in the network.

Configuration Options

Flex IP Solution is customizable for chips of various size and power. All individual TSN and HSR/PRP standards can be enabled or disabled on a per port basis.

- Number of ports (2+1 – 11+1)

- Number of queues (4/8)

- Number of FIDS (0/4/64)

- Number of static FDB entries

- Number of DMA rings

- Clock Frequency (100/125)

- Schedule Table Rows (64-2048)

- Counters (enable/disable)

- Credit-based shapers (enable/disable)

- Gigabit Ethernet (enable/disable)

- HSR RedBox, HSR End Node

- PRP RedBox and DANP support

- HSR-PRP RedBox and QuadBox support

- MII, GMII, RMII, RGMII

- SGMII / 1000BASE-X / 100BASE-FX

- Avalon, AHB, AXI Master (DMA)

- GMII (EMAC)

Time Interface

Ethernet speed interface

- PPS

Application Example

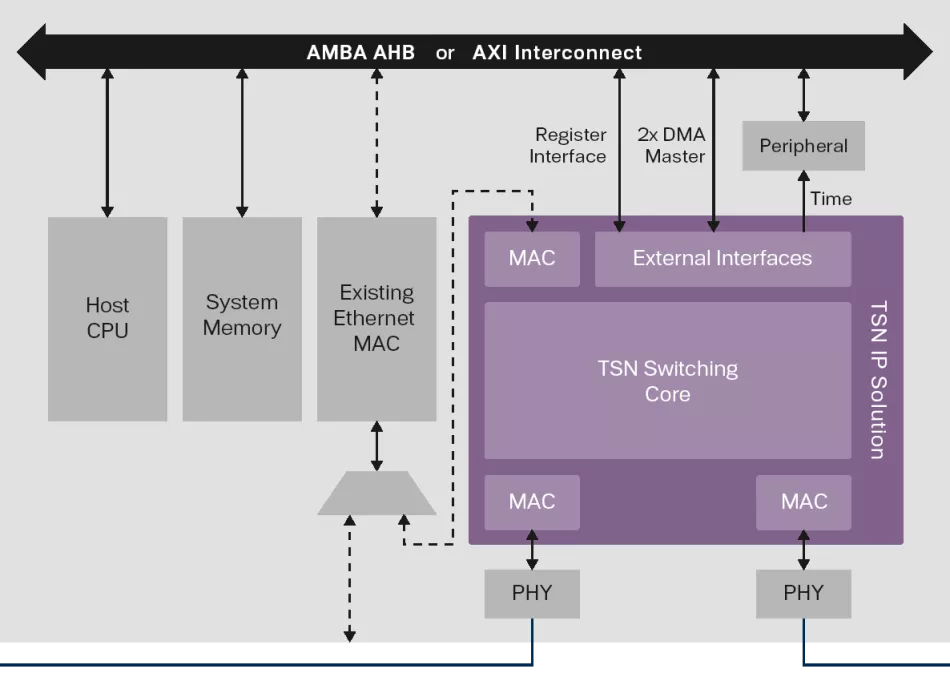

Flex IP Solution provides DMA access for packet transmission, integrated packet timestamping and embedded frame memory. It offers AMBA AHB or AXI bus interfaces.

SoC Integration

TSN Extensions

Acceleration Module

IP hardware extension for switched endpoints

- Adds ultra-low latency communication for TSN networks

- Combines 3 different field-proven technologies: Cut-Through, Summation Frame and Scatter-Gather Engine

- Cut-Through timing ~ 400 ns including data manipulation and under 1 µs per hop including appropriate PHYs

- Achieves cycle times below 10 µs

Technical Specifications

Ports |

3 to 12 ports; 10/100/1000 Mbit/s |

|---|---|

Physical interfaces |

MII, GMII, DMA for host PPS (Pulse-Per-Second) output AXI, Avalon or APB slave interface for management register access AXI or Avalon master interface for DMA to host CPU |

Supported Ethernet Interfaces |

MII, GMII, RMII, RGMII, SGMII, 100BASE-FX, 1000BASE-X |

TSN |

IEEE 802.1AS-2020 Time Synchronization IEEE 802.1Qbv Time Aware Shaping IEEE 802.1Qcc SRP Enhancements IEEE 802.1Qbu Frame Preemption IEEE 802.1CB Frame Replication and Elimination IEEE 802.1Qci Filtering and Policing (Available 2021) |

AVB |

IEEE 802.1AS-2020 Time Synchronization for Time-Sensitive Applications (gPTP) IEEE 802.1Qav Forwarding and Queuing for Time-Sensitive Streams (FQTSS) |

HSR |

HSR RedBox, HSR End Node and QuadBox support |

PRP |

PRP RedBox and DANP support |

IEEE 802.1Q |

Port-based VLANs and VLAN tagging Prioritization of packets on egress ports Untagging of VLAN frames on egress ports |

Clock synchronization |

IEEE 802.1AS-2020 (including multi-time domain support) IEEE 1588-2019 one-step end-to-end transparent clock support |

Switching engine |

Store and forward architecture providing full cross-sectional bandwidth 128-512 kbit frame buffer per port 4096 VLANs, up to 64 MSTIs 16 MAC address filters per port Up to 4096 entry MAC address hash-based learning table Up to 4096 policer per port 8 traffic shapers per port (optional) Static configuration of MAC addresses Flow identification based MAC addresses Ingress rate-limiting on a per-port basis for unicast, multicast, and broadcast traffic |

Embedded software |

Linux kernel module Native Linux interfaces / user space configuration library Edge PTP in binary format for ARM – for IEEE 1588 / IEEE 802.1AS clock synchronization MSTP including additions for engineered traffic (IEEE 802.1Qcc) Open source support for SNMP and NETCONF |